GreenPAK ™

# **Interrupt Controller**

#### **General Description**

Dialog SLG4G42480 is a low power and small form device. The SoC is housed in a 2mm x 2.2mm STQFN package which is optimal for using with small devices.

#### **Features**

- Low Power Consumption

- Pb Free / RoHS Compliant

- Halogen Free

- STQFN 14 Package

#### **Output Summary**

2 Outputs - Open Drain NMOS 1X

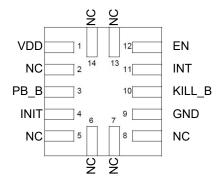

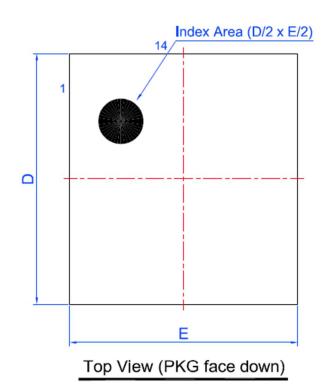

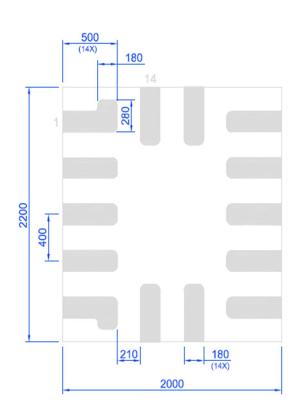

### **Pin Configuration**

**14-pin STQFN** (Top View)

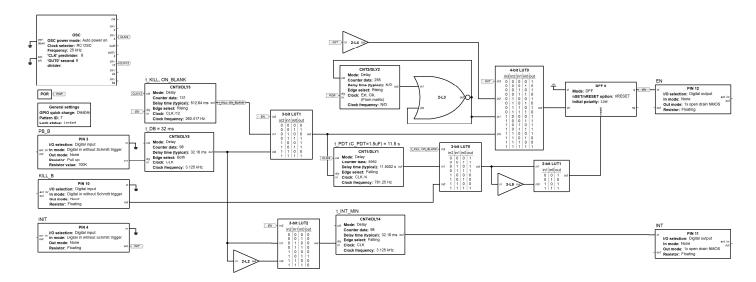

# **Block Diagram**

**Pin Configuration**

| Pin# | Pin Name | Туре           | Type Pin Description                  |              |

|------|----------|----------------|---------------------------------------|--------------|

| 1    | VDD      | PWR            | Supply Voltage                        |              |

| 2    | NC       |                | Keep Floating or Connect to GND       |              |

| 3    | PB_B     | Digital Input  | Digital Input without Schmitt trigger | 100kΩ pullup |

| 4    | INIT     | Digital Input  | Digital Input without Schmitt trigger | floating     |

| 5    | NC       | -              | Keep Floating or Connect to GND       |              |

| 6    | NC       |                | Keep Floating or Connect to GND       |              |

| 7    | NC       |                | Keep Floating or Connect to GND       |              |

| 8    | NC       | -              | Keep Floating or Connect to GND       |              |

| 9    | GND      | GND            | Ground                                |              |

| 10   | KILL_B   | Digital Input  | Digital Input without Schmitt trigger | floating     |

| 11   | INT      | Digital Output | Open Drain NMOS 1X                    | floating     |

| 12   | EN       | Digital Output | Open Drain NMOS 1X                    | floating     |

| 13   | NC       | -              | Keep Floating or Connect to GND       |              |

| 14   | NC       | -              | Keep Floating or Connect to GND       |              |

**Ordering Information**

|               | -                                       |

|---------------|-----------------------------------------|

| Part Number   | Package Type                            |

| SLG4G42480V   | 14-pin STQFN                            |

| SLG4G42480VTR | 14-pin STQFN - Tape and Reel (3k units) |

#### **Absolute Maximum Conditions**

| Parameter                                   | Min. | Max.       | Unit       |    |

|---------------------------------------------|------|------------|------------|----|

| Supply Voltage on VDD relative to 0         | GND  | -0.5       | 7          | V  |

| DC Input Voltage                            |      | GND - 0.5V | VDD + 0.5V | V  |

| Maximum Average or DC Current (Through pin) |      | 8          | mA         |    |

| Current at Input Pin                        | -1.0 | 1.0        | mA         |    |

| Input Leakage (Absolute Value               | )    |            | 1000       | nA |

| Storage Temperature Range                   |      | -65        | 150        | °C |

| Junction Temperature                        |      | 150        | °C         |    |

| ESD Protection (Human Body Mod              | 2000 |            | V          |    |

| ESD Protection (Charged Device M            | 1300 | -          | V          |    |

| Moisture Sensitivity Level                  |      | 1          |            |    |

### **Electrical Characteristics**

| Symbol               | Parameter                                                        | Condition/Note                                             | Min.   | Тур.   | Max.   | Unit |

|----------------------|------------------------------------------------------------------|------------------------------------------------------------|--------|--------|--------|------|

| $V_{DD}$             | Supply Voltage                                                   |                                                            | 3      | 3.3    | 3.6    | V    |

| T <sub>A</sub>       | Operating Temperature                                            |                                                            | -40    | 25     | 85     | °C   |

| $C_VDD$              | Capacitor Value at VDD                                           |                                                            |        | 0.1    |        | μF   |

| CIN                  | Input Capacitance                                                |                                                            |        | 4      |        | pF   |

| ΙQ                   | Quiescent Current                                                | Static inputs and floating outputs. PIN10 and PIN4 are LOW |        | 1      |        | μΑ   |

| Vo                   | Maximal Voltage Applied to<br>any PIN in High-Impedance<br>State |                                                            |        |        | VDD    | V    |

|                      | Maximum Average or DC                                            | T <sub>J</sub> = 85°C                                      |        |        | 45     | mA   |

| $I_{VDD}$            | Current Through VDD Pin (Per chip side, see Note 2)              | T <sub>J</sub> = 110°C                                     |        |        | 22     | mA   |

|                      | Maximum Average or DC                                            | T <sub>J</sub> = 85°C                                      |        |        | 84     | mA   |

| I <sub>GND</sub>     | Current Through GND Pin (Per chip side, see Note 2)              | T <sub>J</sub> = 110°C                                     |        |        | 40     | mA   |

| V <sub>IH</sub>      | HIGH-Level Input Voltage                                         | Logic Input at VDD=3.3V                                    | 1.780  |        |        | V    |

| V <sub>IL</sub>      | LOW-Level Input Voltage                                          | Logic Input at VDD=3.3V                                    |        |        | 1.210  | V    |

| Vol                  | LOW-Level Output Voltage                                         | Open Drain NMOS 1X,<br>I <sub>OL</sub> =3mA, at VDD=3.3V   |        | 0.080  | 0.147  | V    |

| I <sub>OL</sub>      | LOW-Level Output Current (Note 1)                                | Open Drain NMOS 1X,<br>V <sub>OL</sub> =0.4V, at VDD=3.3V  | 7.313  | 12.370 |        | mA   |

| R <sub>PULL_UP</sub> | Internal Pull Up Resistance                                      | Pull up on PIN 3                                           | 70     | 100    | 130    | kΩ   |

|                      |                                                                  | At temperature 25°C                                        | 11.19  | 11.50  | 11.83  | S    |

| T <sub>DLY1</sub>    | Delay1 Time                                                      | At temperature -40 +85°C (Note 3)                          | 10.06  | 11.50  | 13.97  | S    |

|                      |                                                                  | At temperature 25°C                                        | 497.14 | 512.64 | 529.18 | μs   |

| T <sub>DLY3</sub>    | Delay3 Time                                                      | At temperature -40 +85°C (Note 3)                          | 447.11 | 512.64 | 624.75 | μs   |

|                      |                                                                  | At temperature 25°C                                        | 31.14  | 32.16  | 33.26  | μs   |

| T <sub>DLY4</sub>    | Delay4 Time                                                      | At temperature -40 +85°C (Note 3)                          | 28.01  | 32.16  | 39.27  | μs   |

| T <sub>DLY5</sub>    | Delay5 Time                                                      | At temperature 25°C                                        | 31.14  | 32.16  | 33.26  | μs   |

|                     |                     | At temperature -40 +85°C (Note 3)                      | 28.01 | 32.16 | 39.27 | μs |

|---------------------|---------------------|--------------------------------------------------------|-------|-------|-------|----|

| T <sub>SU</sub>     | Startup Time        | from VDD rising past 1.35 V                            | -     | 0.3   |       | ms |

| PONTHR              | Power On Threshold  | V <sub>DD</sub> Level Required to Start<br>Up the Chip | 1.096 | 1.353 | 1.528 | V  |

| POFF <sub>THR</sub> | Power Off Threshold | V <sub>DD</sub> Level Required to Switch Off the Chip  | 0.759 | 0.933 | 1.125 | V  |

#### Note

- 1. DC or average current through any pin should not exceed value given in Absolute Maximum Conditions.

- 2. The GreenPAK's power rails are divided in two sides. Pins 2, 3, 4, 5, 6, 7 and 8 are connected to one side, pins 10, 11, 12, 13 and 14 to another.

- 3. Guaranteed by Design.

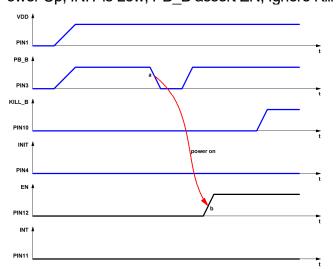

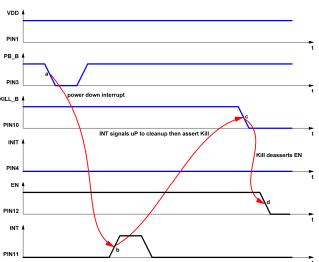

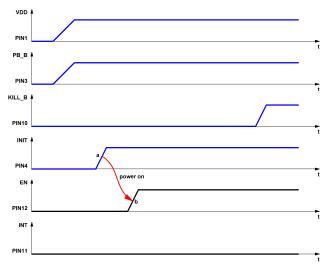

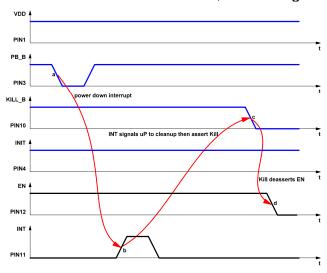

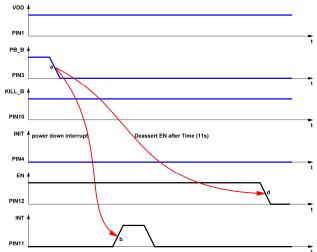

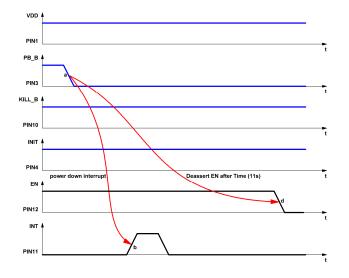

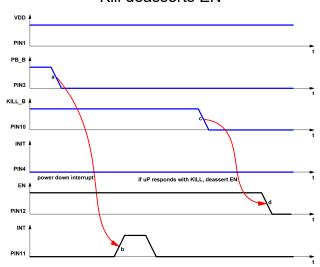

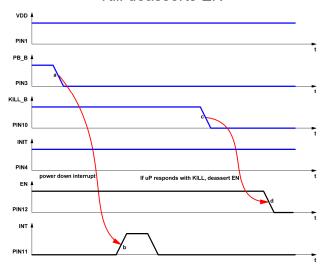

### **Timing Diagram**

Power Up, INIT is Low, PB\_B assert EN, Ignore Kill

Power Down via Short Push, INIT is Low

Power Up, INIT is High, Assert EN, Ignore Kill

Power Down via Short Push, INIT is High

#### Power Down via Long Push, INIT is Low, No Kill

Power Down via Long Push, INIT is High, No Kill

#### Power Down via Long Push, INIT is Low, Kill deasserts EN

#### Power Down via Long Push, INIT is High, Kill deasserts EN

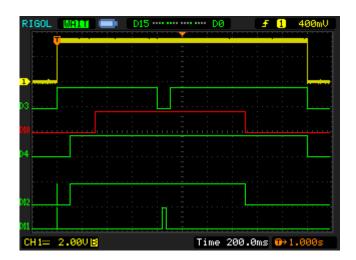

#### **Functionality Waveforms**

Channel 1 (yellow/top line) - PIN# 1 (VDD)

D3 – PIN#3 (PB B)

D4 – PIN#4 (INIT)

D10 - PIN#10 (KILL B)

D11 – PIN#11 (INT) with external  $5k\Omega$  pull up resistor

D12 – PIN#12 (EN) with external  $5k\Omega$  pull up resistor

1. Power Up, INIT is Low, PB\_B assert EN, Ignore Kill and Power Down via Short Push, INIT is Low

2. Power Up, INIT is High, Assert EN, Ignore Kill and Power Down via Short Push, INIT is High

3. Power Up, INIT is Low, PB\_B assert EN, Ignore Kill and Power Down via Long Push, INIT is low, No Kill

4. Power Up, INIT is High, Assert EN, Ignore Kill and Power Down via Long Push, INIT is high, No Kill

Channel 1 (yellow/top line) - PIN# 1 (VDD)

D3 - PIN#3 (PB\_B)

D4 - PIN#4 (INIT)

D10 - PIN#10 (KILL B)

D11 – PIN#11 (INT) with external  $5k\Omega$  pull up resistor

D12 – PIN#12 (EN) with external  $5k\Omega$  pull up resistor

5. Power Up, INIT is Low, PB\_B assert EN, Ignore Kill and Power Down via Long Push, INIT is low, Kill deasserts EN

6. Power Up, INIT is High, Assert EN, Ignore Kill and Power Down via Long Push, INIT is high, Kill deasserts EN

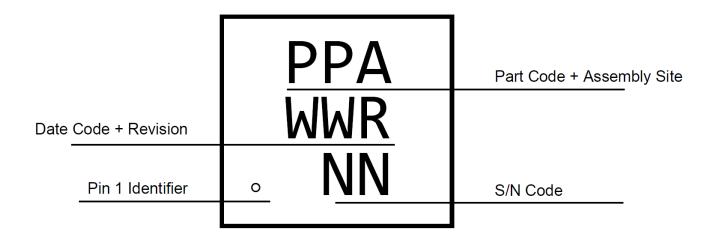

### **Package Top Marking**

| Datasheet<br>Revision | Programming Code Number | Lock<br>Status | Checksum   | Part<br>Code | Revision | Date       |

|-----------------------|-------------------------|----------------|------------|--------------|----------|------------|

| 1.00                  | 007                     | L              | 0x38C0C0BD | A5           | Ш        | 04/25/2019 |

The IC security bit is locked/set for code security for production unless otherwise specified. Revision number is not changed for bit locking.

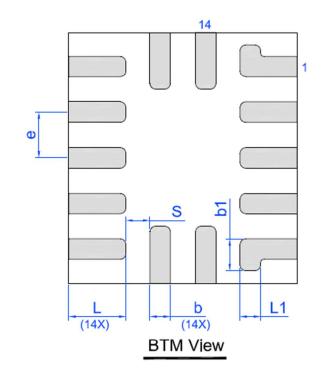

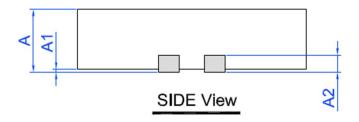

# **Package Drawing and Dimensions**

#### STQFN 14L 2 x 2.2mm 0.4P COL Package JEDEC MO-220, Variation WECE

#### Unit: mm

| Symbol | Min      | Nom. | Max   | Symbol | Min      | Nom.     | Max  |

|--------|----------|------|-------|--------|----------|----------|------|

| Α      | 0.50     | 0.55 | 0.60  | D      | 2.15     | 2.20     | 2.25 |

| A1     | 0.005    | -    | 0.050 | Е      | 1.95     | 2.00     | 2.05 |

| A2     | 0.10     | 0.15 | 0.20  | L      | 0.45     | 0.50     | 0.55 |

| b      | 0.13     | 0.18 | 0.23  | S      | (        | 0.21 TYP |      |

| е      | 0.40 BSC |      |       | b1     | 0.28 TYP |          |      |

|        |          |      | _     | L1     | (        | 0.18 TYP |      |

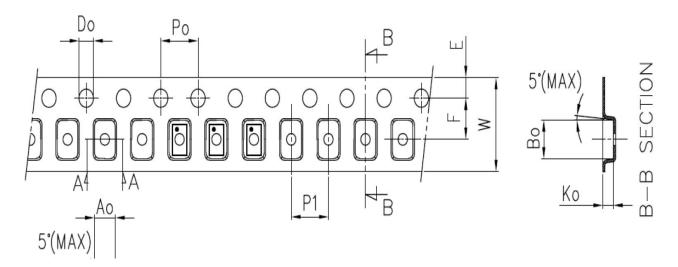

### **Tape and Reel Specification**

| Package                                | # of | Nominal              | Max Units |         | Reel & Hub | Leader (min) |                | Trailer (min) |                | Tape<br>Width | Part<br>Pitch |

|----------------------------------------|------|----------------------|-----------|---------|------------|--------------|----------------|---------------|----------------|---------------|---------------|

| Type                                   | Pins | Package Size<br>[mm] | per Reel  | per Box | Size [mm]  | Pockets      | Length<br>[mm] | Pockets       | Length<br>[mm] | [mm]          | [mm]          |

| STQFN<br>14L<br>2x2.2mm<br>0.4P<br>COL | 14   | 2x2.2x0.55           | 3000      | 3000    | 178/60     | 100          | 400            | 100           | 400            | 8             | 4             |

### **Carrier Tape Drawing and Dimensions**

| Package<br>Type                      | Pocket<br>BTM<br>Length | Pocket<br>BTM<br>Width | Pocket<br>Depth<br>K0 | Index<br>Hole<br>Pitch | Pocket<br>Pitch | Index<br>Hole<br>Diameter | Index<br>Hole to<br>Tape Edge | Index<br>Hole to<br>Pocket<br>Center | Tape<br>Width |

|--------------------------------------|-------------------------|------------------------|-----------------------|------------------------|-----------------|---------------------------|-------------------------------|--------------------------------------|---------------|

| STQFN<br>14L 2x2.2<br>mm 0.4P<br>COL | 2.2                     | 2.35                   | 0.8                   | 4                      | 4               | 1.5                       | 1.75                          | 3.5                                  | 8             |

# **Recommended Reflow Soldering Profile**

Please see IPC/JEDEC J-STD-020: latest revision for reflow profile based on package volume of 2.42 mm<sup>3</sup> (nominal). More information can be found at <a href="https://www.jedec.org">www.jedec.org</a>.

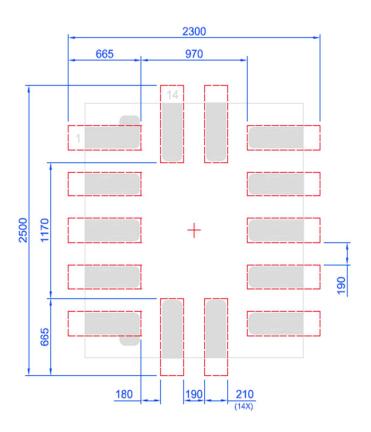

#### **Recommended Land Pattern**

Exposed Pad (PKG face down)

Recommended Land Pattern (PKG face down)

Unit:um

# **Datasheet Revision History**

| Date       | Version | Change                                                                   |

|------------|---------|--------------------------------------------------------------------------|

| 05/08/2018 | 0.10    | New design for SLG46170 chip                                             |

| 05/25/2018 | 0.11    | Implemented invariable INTERRUPT period. Added ON_BLANK functionality to |

|            |         | correct KILL_B work                                                      |

| 05/30/2018 | 0.12    | Updated Device Revision Table                                            |

| 06/27/2018 | 0.13    | Added INIT-pin to select start-up logic                                  |

| 06/29/2018 | 0.14    | Updated Device Revision Table                                            |

| 07/02/2018 | 0.15    | Changed the name of PIN 11 (INT_B to INT)                                |

| 07/18/2018 | 0.16    | Corrected INIT-functionality                                             |

| 07/20/2018 | 0.17    | Updated Device Revision Table                                            |

| 08/08/2018 | 0.18    | Corrected functionality of KILL_B                                        |

| 08/08/2018 | 0.19    | Updated Device Revision Table                                            |

| 11/20/2018 | 0.20    | Fixed the issue of the INIT-function                                     |

| 04/15/2019 | 0.21    | Updated Lock-Status                                                      |

| 04/25/2019 | 1.00    | Production Release                                                       |

|            |         |                                                                          |

#### **Disclaimer**

Information in this document is believed to be accurate and reliable. However, Dialog Semiconductor does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information. Dialog Semiconductor furthermore takes no responsibility whatsoever for the content in this document if provided by any information source outside of Dialog Semiconductor.

Dialog Semiconductor reserves the right to change without notice the information published in this document, including without limitation the specification and design of the related semiconductor products, software and applications.

Applications, software, and semiconductor products described in this document are for illustrative purposes only. Dialog Semiconductor makes no representation or warranty that such applications, software and semiconductor products will be suitable for the specified use without further testing or modification. Unless otherwise agreed in writing, such testing or modification is the sole responsibility of the customer and Dialog Semiconductor excludes all liability in this respect.

Customer notes that nothing in this document may be construed as a license for customer to use the Dialog Semiconductor products, software and applications referred to in this document. Such license must be separately sought by customer with Dialog Semiconductor.

All use of Dialog Semiconductor products, software and applications referred to in this document are subject to Dialog Semiconductor's Standard Terms and Conditions of Sale, available on the company website (www.dialog-semiconductor.com) unless otherwise stated.

Dialog and the Dialog logo are trademarks of Dialog Semiconductor plc or its subsidiaries. All other product or service names are the property of their respective owners.

© 2018 Dialog Semiconductor. All rights reserved.

### **RoHS Compliance**

Dialog Semiconductor's suppliers certify that its products are in compliance with the requirements of Directive 2011/65/EU of the European Parliament on the restriction of the use of certain hazardous substances in electrical and electronic equipment. RoHS certificates from our suppliers are available on request

### **Contacting Dialog Semiconductor**

United Kingdom (Headquarters)

Dialog Semiconductor (UK) LTD

Phone: +44 1793 757700

Germany

Dialog Semiconductor GmbH Phone: +49 7021 805-0

**The Netherlands**

Dialog Semiconductor B.V. Phone: +31 73 640 8822

**Email**

enquiry@diasemi.com

**North America**

Dialog Semiconductor Inc. Phone: +1 408 845 8500

Japan

Dialog Semiconductor K. K. Phone: +81 3 5769 5100

**Taiwan**

Dialog Semiconductor Taiwan Phone: +886 281 786 222

Web site:

www.dialog-semiconductor.com

**Hong Kong**

Dialog Semiconductor Hong Kong Phone: +852 2607 4271

Korea

Dialog Semiconductor Korea Phone: +82 2 3469 8200 China (Shenzhen)

Dialog Semiconductor China Phone: +86 755 2981 3669

China (Shanghai)

Dialog Semiconductor China Phone: +86 21 5424 9058